# Baseband Impedance and Linearization of FET Circuits

James Brinkhoff, *Student Member, IEEE*, Anthony Edward Parker, *Senior Member, IEEE*, and Martin Leung, *Student Member, IEEE*

**Abstract**—Baseband impedance has been identified as having a positive or negative effect on the intermodulation distortion of microwave circuits. The effect can be assessed or utilized with the aid of previously proposed figures-of-merit. Under certain situations, intermodulation cancellation can be achieved simply by adding resistance to the bias network. The impact of baseband impedance on the performance of derivative superposition amplifiers is analyzed. A bias region was studied that exhibits a good second- and third-order intermodulation null with minimal intermodulation dependence on baseband impedance. This allows the effective use of the derivative superposition technique in baseband amplifiers, as well as giving wide-band linearization performance in RF amplifiers.

**Index Terms**—Field-effect transistor (FET) amplifiers, harmonic distortion, impedance, intermodulation distortion, linearization, memory effects.

## I. INTRODUCTION

MODERN communications systems are using wide bandwidths, necessitating the efficient use of the available spectrum. Thus, there is increasing demand for wide-band linear amplifiers for use in transmitters and receivers. It is desirable that high linearity be achieved with minimal circuit complexity, power usage, and cost, especially in the growing mobile device market.

A number of circuit-level methods have been developed to meet these needs. These include terminating impedance optimization [1], predistortion [2], second-order distortion injection [3], and derivative superposition [4].

A fundamental obstacle to developing amplifiers that are highly linear over wide bandwidths is caused by long time-constant *memory* effects. These effects cause the distortion levels to change depending on the bandwidth of the signal being amplified. They can be clearly observed by measuring two-tone intermodulation over varying tone spacing. While the above linearization methods can be effective at small bandwidths, their performance often rapidly degrades as the signal bandwidth increases [5].

Memory effects are caused by both device and circuit mechanisms. This study concentrates on memory effects caused by baseband impedance. Bias networks in microwave circuits are a common cause of baseband impedance change with frequency. It has been shown that baseband impedance can cause asymmetry in intermodulation levels under certain conditions [6],

Manuscript received April 15, 2003. The work of J. Brinkhoff was supported under an Australian Postgraduate Award.

The authors are with the Department of Electronics, Macquarie University, Sydney, Australia 2109 (e-mail: james\_b@ieee.org).

Digital Object Identifier 10.1109/TMTT.2003.819208

and that it can cause the intermodulation levels to change with varying tone spacing [7].

Previously, we have shown that a field-effect transistor (FET) can be biased such that the baseband impedance has little effect on intermodulation and, hence, memoryless predistortion linearization can be effective over wide bandwidths [8]. A summary of the relevant results from [7] and [8] is given in Section II. Throughout this study, the analysis and measurements concern circuits with low signal levels so that the distortion can be described by weakly nonlinear behavior. In Section III, a method to linearize an FET amplifier at certain biases, simply by changing the baseband impedance, is developed. Section IV analyzes the effects of baseband impedance on derivative superposition amplifiers and proposes a method to find a bias that reduces the effects. This is shown to be important in two applications: low-distortion baseband amplifiers and RF amplifiers requiring linearity over wide bandwidths.

## II. INTERMODULATION MODEL

An analysis has been previously developed to predict the effects of baseband impedance on intermodulation [7]. This analysis is valid for an FET in the common-source configuration with a two-tone input signal, where the impedance presented to the drain of the FET is  $Z_d(\omega)$ . It is assumed that the input signal is small enough that distortion terms above third order can be neglected. In addition, we assume that the frequencies are such that the distortion can be adequately modeled by considering only the nonlinear drain current. The results from the analysis are summarized and developed in this section for completeness.

In [7], the drain current is described by a two-dimensional Taylor series

$$i_d = G_m v_g + G_d v_d + G_{m2} v_g^2 + G_{md} v_g v_d + G_{d2} v_d^2 + G_{m3} v_g^3 + G_{m2d} v_g^2 v_d + G_{md2} v_g v_d^2 + G_{d3} v_d^3. \quad (1)$$

Suppose that  $v_g$  is a two-tone signal, the magnitude of each tone being  $V_s$ , so that

$$v_g = 2V_s \cos(\omega_c t) \cos\left(\frac{\Delta\omega_c t}{2}\right). \quad (2)$$

The magnitude of the first-order component of the output voltage at the fundamental frequencies is

$$V_{d1} = -V_s G_m Z_o(\omega_c) \quad (3)$$

where

$$Z_o(\omega) = \frac{Z_d(\omega)}{1 + G_d Z_d(\omega)} \quad (4)$$

is the drain conductance in parallel with the drain termination and  $G_m$  and  $G_d$  are the first-order transconductance and drain conductance, respectively.

The magnitude of the third-order output voltage at the intermodulation frequencies is

$$V_{d3} = V_s^3 Z_o(\omega_c) (c_0 Z_o(\Delta\omega) + c_1 + c_2 Z_o(2\omega_c)) \quad (5)$$

where  $c_0$ ,  $c_1$ , and  $c_2$  are defined in [7] and reproduced in the Appendix. They depend on the impedance at the fundamental frequency only, and change with bias because they involve the nine coefficients of the nonlinear drain current (1).

The intermodulation depends not only on the fundamental frequency drain impedance, but also on the baseband and second harmonic drain impedance, as seen in the terms  $c_0 Z_o(\Delta\omega)$  and  $c_2 Z_o(2\omega_c)$  in (5). The equation is valid for any frequency-dependent drain impedance.

Two figures-of-merit have been proposed in [8] for selection of a device and bias based on distortion performance. These figures-of-merit are an assessment of the intermodulation level and the effect of baseband impedance on intermodulation. They model the low-frequency behavior of a device accurately, and have been previously shown to predict the overall trends of the intermodulation at high frequencies as well. They are very useful when computed over a range of biases.

The first figure-of-merit, i.e., IM3, is the intermodulation level relative to the fundamental level (dBc) with zero baseband drain termination ( $Z_d(\Delta\omega) = 0$ , typical for  $LC$  bias networks at small tone spacings). With reference to (3) and (5), this quantity is

$$IM3 = 20 \log \left| \frac{V_s^2 (c_1 + c_2 Z_o(2\omega_c))}{G_m} \right| \text{ dBc.} \quad (6)$$

The second figure-of-merit, i.e.,  $\Delta IM3$ , gives an indication of the intermodulation change that occurs when the baseband impedance changes from zero to some other value  $Z_b$ . The equation for this is

$$\Delta IM3 = 20 \log \left| \frac{Z_b}{(1 + G_d Z_b)} \frac{c_0}{(c_1 + c_2 Z_o(2\omega_c))} + 1 \right| \text{ dB} \quad (7)$$

where  $Z_b$  is the nominal load, which, for this study, is  $50 \Omega$ . Thus, for typical  $LC$  bias networks,  $\Delta IM3$  indicates the change in the intermodulation levels as the baseband impedance changes from  $0 \Omega$  at small tone spacings to the load impedance at large tone spacings. These figures-of-merit can be found by simulation using (6) and (7) or by measurement, as will be discussed in Section IV-B.

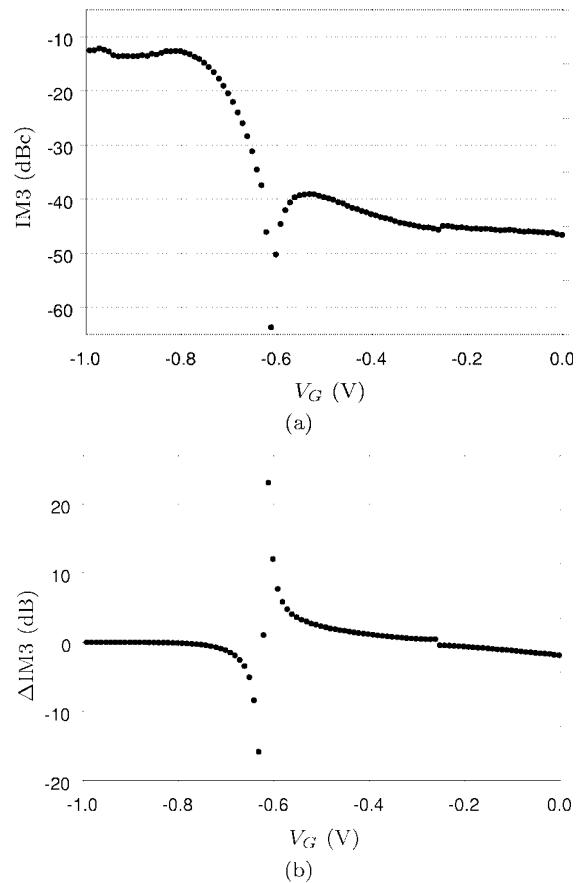

This study uses Agilent ATF-35143 packaged pseudomorphic high-electron-mobility transistors (pHEMTs), which have a threshold voltage of approximately  $-0.7$  V. The coefficients of nonlinear drain current (1) were extracted using a method similar to that in [9]. The figures-of-merit for a typical device are shown in Fig. 1, which were calculated using (6) and (7). The characteristic intermodulation null is at  $V_G \approx -0.6$  V. At this point, there is also large intermodulation susceptibility to

Fig. 1. Predicted figures-of-merit [(6) and (7)] versus gate bias for an ATF-35143 pHEMT with  $V_D = 2$  V and  $Z_d(\omega_c) = 50 \Omega$ . The lower tone is at 50 MHz and the input signal has a peak voltage of  $V_s = 0.1$  V. (a) IM3—intermodulation with  $Z_d(\Delta\omega) = 0$ . (b)  $\Delta IM3$ —change in intermodulation when  $Z_d(\Delta\omega)$  changes from 0 to  $50 \Omega$ .

baseband impedance, as explained in [8]. The small discontinuity near  $V_G \approx -0.3$  V is due to harmonic distortion from the signal generators used in characterization, not to the device.

### III. BASEBAND IMPEDANCE LINEARIZATION

It is clear from Fig. 1(b) that, at certain biases, the intermodulation levels will be lower if the baseband drain impedance is nonzero. Thus, the common practice of setting the baseband impedance in power amplifiers to zero is not always optimal. This has also been observed in [10]. The optimum baseband impedance  $Z_d(\Delta\omega) = Z_{b_{\text{opt}}}$  can be found by solving

$$c_0 Z_o(\Delta\omega) + c_1 + c_2 Z_o(2\omega_c) = 0 \quad (8)$$

from (5), where  $Z_o$  is given in terms of  $Z_d$  in (4). This yields

$$Z_{b_{\text{opt}}} = - \left( \frac{c_1 + c_2 Z_o(2\omega_c)}{c_0 + G_d(c_1 + c_2 Z_o(2\omega_c))} \right). \quad (9)$$

Over most gate biases, the value for  $Z_{b_{\text{opt}}}$  that cancels the intermodulation is negative and, hence, this technique is not useful. However, in the regions where  $\Delta IM3$  is large and negative (typically just above pinchoff), the optimum baseband impedance is positive and, thus, it would be expected that significant intermodulation cancellation can be achieved at

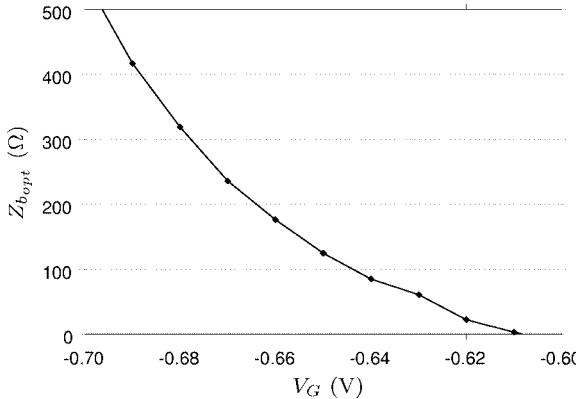

Fig. 2. Baseband impedance for intermodulation cancellation  $Z_{b,\text{opt}}$  for a typical ATF-35143 pHEMT with  $V_D = 2$  V.

these biases. Any imaginary component in the fundamental or second harmonic drain impedances will decrease the level and bandwidth of intermodulation cancellation. The baseband impedance can be varied by adding a series resistance to the inductor that supplies the drain bias. This will not alter the gain of the amplifier. A graph showing the optimum  $Z_{b,\text{opt}}$  over the useful bias range is shown in Fig. 2.

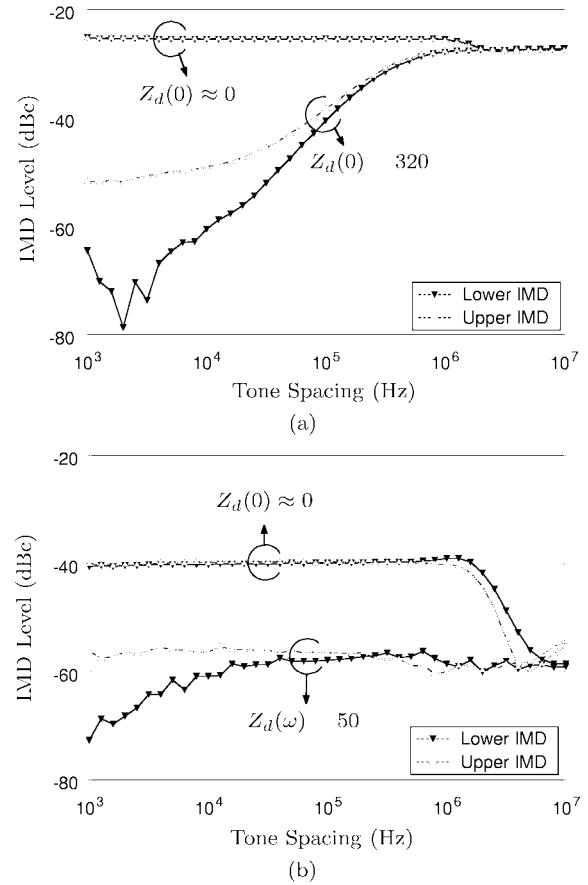

At  $V_G = -0.68$  V, the optimum baseband impedance is  $320 \Omega$ . The intermodulation levels with this baseband impedance and those with zero baseband impedance are compared in Fig. 3(a). It can be seen that over 20 dB of linearization has been achieved. However, this rapidly degrades as the tone spacing increases because the baseband impedance changes from  $320 \Omega$  at small tone spacings to  $50 \Omega$  at large tone spacings. Hence, this technique can be useful for amplifiers of small bandwidth signals, where the baseband impedance will not change over the required bandwidth.

There is a bias where  $Z_{b,\text{opt}} = 50 \Omega$ , somewhere between  $V_G = -0.63$  and  $-0.62$  V for the device in Fig. 2. A bias network can be designed such that the impedance from baseband up to RF frequencies is constant. That is, the impedance at the drain will be  $50 \Omega$  over all frequencies. This is achieved using an *LC* bias network, with a  $50\text{-}\Omega$  resistor in series with the inductor and the capacitance set to  $C = L/R^2$ .

The intermodulation levels with the constant  $50\text{-}\Omega$  network are shown in Fig. 3(b). The optimum gate bias with  $Z_d(\omega) = 50 \Omega$  was adjusted while monitoring the IM3 levels. Over 15 dB of improvement is obtained compared to the levels with  $Z_d(0) = 0$ . The linearized intermodulation characteristics are relatively constant over a wide bandwidth because the load impedance is constant from baseband to RF. This technique could also be useful in baseband amplifiers, where the baseband impedance is equal to the carrier-frequency impedance. A limitation of this technique is that cancellation depends critically on the bias point. For example, the linearization may be negligible if the gate bias changes over 10 mV, as implied by Fig. 1(a). It may be possible to make this technique robust by using adaptive bias control.

#### IV. DERIVATIVE SUPERPOSITION

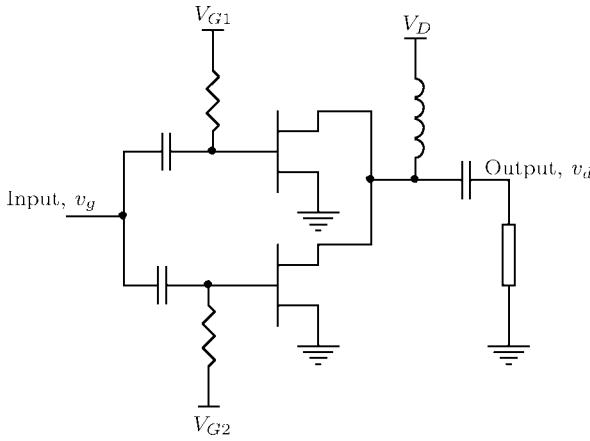

The derivative superposition amplifier has emerged as a useful linearization technique [4]. It is conceptually simple, requires no complex circuit tuning techniques, does not involve

Fig. 3. Measured baseband impedance linearization of a pHEMT amplifier with  $V_D = 2$  V and  $Z_d(\omega_c) = 50 \Omega$ . The lower tone is at 50 MHz and the input signal has a peak voltage of  $V_s = 0.1$  V. (a)  $V_G = -0.68$  V,  $Z_d(\Delta\omega) = 320 \Omega$  for small  $\Delta\omega$ ,  $50 \Omega$  for large  $\Delta\omega$ . (b)  $V_G \approx -0.62$  V,  $Z_d(\Delta\omega) = 50 \Omega$  for all  $\omega$ .

a significant increase in circuit complexity, and achieves good performance. The analysis and results presented here considers all the terms in the drain current (1) for an understanding of how baseband, second harmonic, and fundamental-frequency impedance will affect the performance of derivative superposition amplifiers.

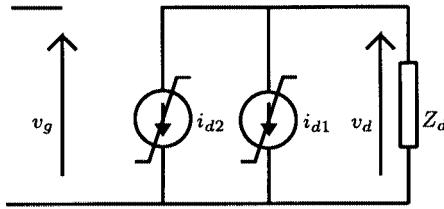

#### A. Derivative Superposition Amplifier Intermodulation

The circuit diagram of a typical derivative superposition amplifier is shown in Fig. 4. At low frequencies, a two-transistor amplifier can be represented by the equivalent circuit in Fig. 5. Each FET is represented by a two-port voltage-controlled current source. Each current source can be modeled by a Taylor series, as in (1). However, the transistors have different biases so the Taylor-series coefficients will be different for each transistor. If the drain current of the first transistor is  $i_{d1}$ , and that of the second is  $i_{d2}$ , the total drain current is

$$\begin{aligned}

i_d &= i_{d1} + i_{d2} \\

&= (G_{m1} + G_{m2}) v_g + (G_{d1} + G_{d2}) v_d \\

&\quad + (G_{m21} + G_{m22}) v_g^2 + (G_{md1} + G_{md2}) v_g v_d \\

&\quad + (G_{d21} + G_{d22}) v_d^2 + (G_{m31} + G_{m32}) v_g^3 \\

&\quad + (G_{m2d1} + G_{m2d2}) v_g^2 v_d + (G_{md21} + G_{md22}) v_g v_d^2 \\

&\quad + (G_{d31} + G_{d32}) v_d^3. \tag{10}

\end{aligned}$$

Fig. 4. Derivative superposition amplifier.

Fig. 5. Low-frequency equivalent circuit of a derivative superposition amplifier.

Thus, the intermodulation analysis of a derivative superposition is the same as that of a single FET amplifier, as presented in [7], except that each coefficient in the Taylor-series expansion of the drain current is replaced by the sum of that coefficient in the first and second transistor. Therefore, to analyze the intermodulation distortion of a derivative superposition amplifier, (5) is valid, provided the above substitutions are performed. The coefficients  $c_0$ ,  $c_1$ , and  $c_2$  are now two-dimensional functions of bias, as they depend on the bias of two transistors.

An important consequence of the fact that a derivative superposition amplifier's intermodulation can be modeled with (5) concerns complex drain impedances. If the impedance presented to the drain of the device (including the effect of the drain-source capacitance) has a significant imaginary component at the fundamental frequency, the effectiveness of the intermodulation cancellation will be reduced. This is because the real and imaginary parts of (5) may not be zero at the same bias. It might be expected that conjugate matching will eliminate this problem because the imaginary terms in the drain impedance are cancelled. However, if  $c_2$  is not negligible (as is the case for a conventionally biased amplifier), the drain impedance must be real at the fundamental and second harmonic frequencies. Therefore, careful design of the matching network at the drain of the device is required at high frequencies.

If only the transconductance terms ( $G_m$ ,  $G_{m2}$ , and  $G_{m3}$ ) of the drain current model are considered, then  $c_1$  in (5) simplifies to  $G_{m3} = G_{m31} + G_{m32}$ . In addition,  $c_0 = c_2 = 0$  (see Appendix). In this case, there are no baseband impedance effects, and the optimum biases for the transistors are simply those that give  $G_{m31} + G_{m32} \approx 0$  over the greatest range of gate voltages, which gives a wide intermodulation null. However, in a

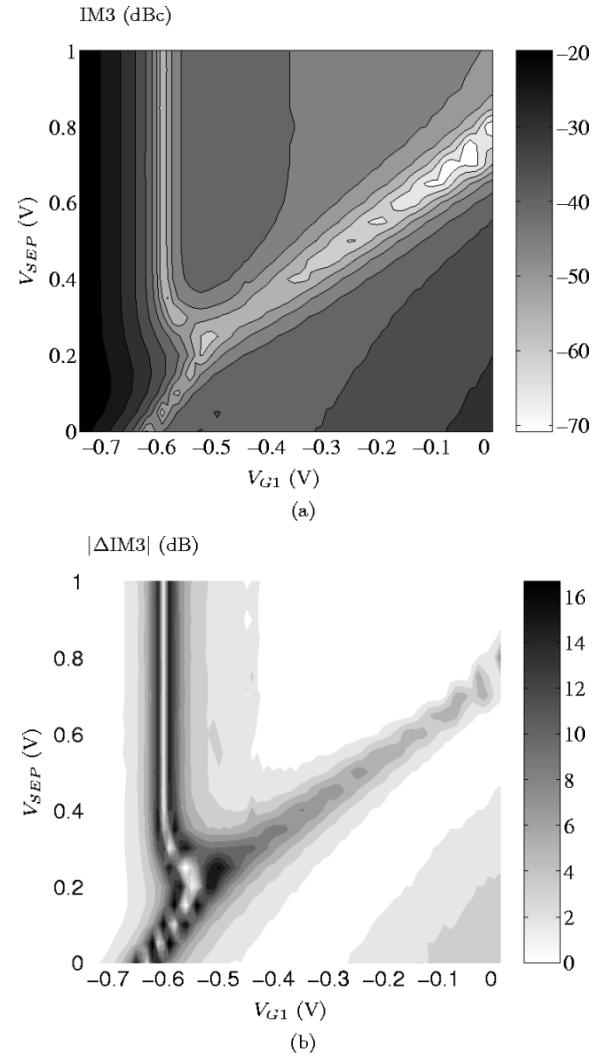

Fig. 6. Measured figures-of-merit versus primary gate bias and bias separation for a derivative superposition amplifier with  $V_D = 2$  V and  $Z_d(\omega_c) = 50 \Omega$ . The lower tone is at 50 MHz and the input signal has a peak voltage of  $V_s = 0.11$  V. (a) IM3—intermodulation (dBc) with  $Z_d(\Delta\omega) = 0$ . (b)  $|\Delta\text{IM3}|$ —change in intermodulation (dB) when  $Z_d(\Delta\omega)$  changes from 0 to  $50 \Omega$ .

real device, the cross and conductance terms in the drain current are significant. They cannot be neglected if an understanding of how the intermodulation will change with drain impedance at fundamental, baseband, and second-harmonic frequencies is required.

A typical derivative superposition amplifier is implemented with the two transistors biased on opposite sides of the third-order intermodulation (IM3) null in Fig. 1(a). This will give a wider intermodulation null because the sign of the intermodulation is different on either side of the null [4]. However, the second-order terms are large and positive on both sides of the null. Thus, the IM3 cancellation is at the expense of increased second-order distortion. This is usually not considered to be a problem when second-order products are out-of-band. However,  $c_0$  is dependent on the second-order terms and, thus, it will be large. Therefore, for a typical derivative superposition amplifier, the intermodulation will change markedly with changes in the baseband impedance. This limits the bandwidth of effective linearization. A technique to solve

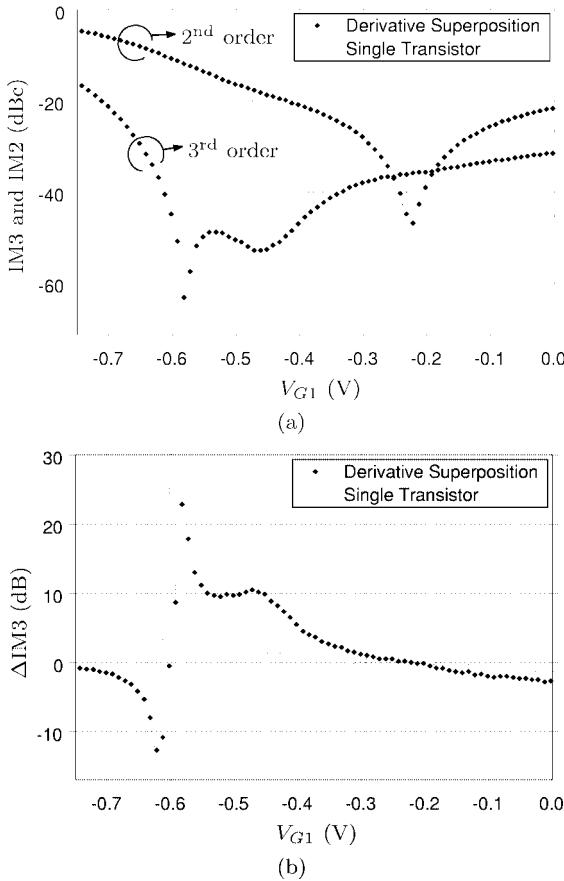

Fig. 7. Measured figures-of-merit for the conventionally biased derivative superposition amplifier under the same conditions as Fig. 6. The derivative superposition result is at  $V_{SEP} = 0.3$  V and the single transistor result has the second transistor pinched off at  $V_{SEP} = 1.5$  V. (a) IM3 and IM2. (b)  $\Delta IM3$ .

this problem, explored below, involves biasing the devices to cancel second- and third-order distortion simultaneously.

#### B. Characterizing a Derivative Superposition Amplifier

A derivative superposition amplifier using two ATF-35143 pHEMTs was constructed. The bias network was designed with impedance at 10 kHz close to  $0\ \Omega$ , and impedance at 20 MHz approximately  $50\ \Omega$ . This allowed the measurement of the two figures-of-merit, i.e., IM3 and  $\Delta IM3$ . IM3 is simply the intermodulation distortion with a tone spacing of 10 kHz, where there is negligible baseband impedance.  $\Delta IM3$  is the difference between the distortion at a tone spacing of 20 MHz and that at 10 kHz, which is the difference between the distortion for a baseband impedance of 50 and  $0\ \Omega$ . The lower tone was 50 MHz and input tone peak voltages were 0.11 V.

In this case, IM3 and  $\Delta IM3$  are two-dimensional functions because they depend on the biases of two devices. They are plotted against the gate bias of the primary device  $V_{G1}$  on one axis, and the difference between the biases of the primary and secondary device  $V_{SEP} = V_{G1} - V_{G2}$  on the other axis, as shown in Fig. 6.

In Fig. 6(a), the null at  $V_G = -0.6$  V is observed when the second transistor is well into pinchoff ( $V_{G2} < -1$  V or  $V_{SEP} > 0.4$  V) so that the amplifier is essentially operating as a single-transistor amplifier. This corresponds to the null at this bias for a single transistor, as shown in Fig. 1. The baseband impedance

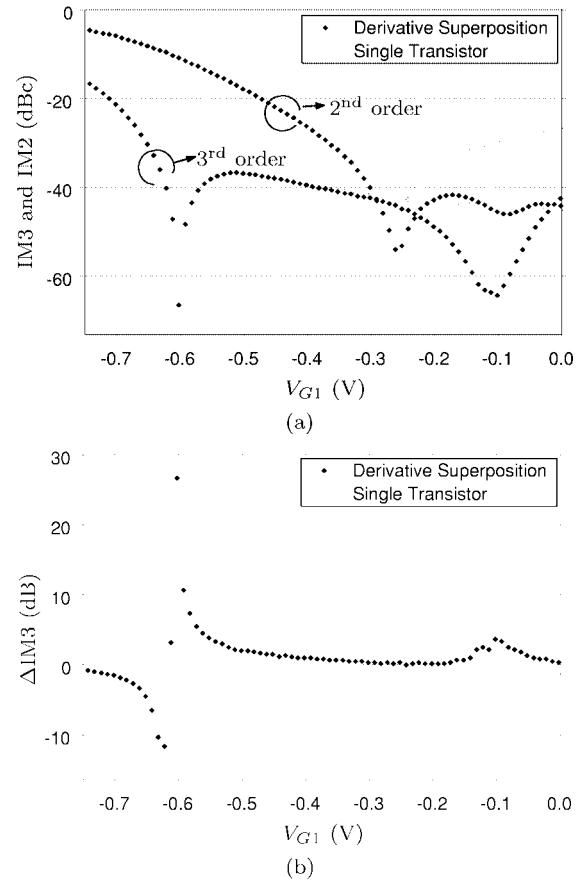

Fig. 8. Measured figures-of-merit for the low  $\Delta IM3$  biased derivative superposition amplifier under the same conditions as Fig. 6. The derivative superposition result is at  $V_{SEP} = 0.65$  V and the single transistor result has the second transistor pinched off at  $V_{SEP} = 1.5$  V. (a) IM3 and IM2. (b)  $\Delta IM3$ .

susceptibility is large in this region, as evidenced by significant  $\Delta IM3$ .

As the second transistor comes out of pinchoff, the typical derivative superposition action starts to occur. When the primary gate bias is at  $V_{G1} = -0.5$  V and the voltage separation is  $V_{SEP} = 0.3$  V ( $V_{G2} = -0.8$  V), there is a  $>150$ -mV-wide null, as seen in Fig. 6(a). The distortion of the single transistor amplifier (with the second transistor pinched off) and the distortion of the derivative superposition amplifier with constant bias voltage separation of 0.3 V, are compared in Fig. 7(a). This is the conventional bias where a derivative superposition amplifier would normally be operated. However,  $\Delta IM3$  is large in this region, as seen in Fig. 7(b), thus, baseband impedance susceptibility will be high. The significant  $\Delta IM3$  in the vicinity of the null can be explained by the large second-order distortion in this region, as shown in Fig. 7(a), remembering that  $\Delta IM3$  depends on  $c_0$ , which depends on second-order nonlinearity. Thus, this bias will not be good for amplifiers requiring linearity for wide-bandwidth signals with conventional bias networks.

However, this is not the only bias where a wide intermodulation null is achieved. Fig. 6(a) shows that there is a wide null along the diagonal line  $V_{SEP} = V_{G1} + 0.75$ , ( $V_{G2} = -0.75$  V). Thus, if the secondary transistor has a gate bias of  $-0.75$  V, there will be a null in the intermodulation characteristics for any  $V_{G1} > -0.5$  V. It can also be seen that  $\Delta IM3$  is smaller for higher  $V_{G1}$ . This is a consequence of the fact that there is a

TABLE I

COEFFICIENTS OF NONLINEAR DRAIN CURRENT FOR THE ATF-35143 pHEMT WITH  $V_D = 2$  V. THE COEFFICIENTS FOR BOTH THE CONVENTIONAL ( $V_{G1} = -0.5$  V,  $V_{SEP} = 0.3$  V) AND Low  $\Delta\text{IM3}$  ( $V_{G1} = -0.1$  V,  $V_{SEP} = 0.65$  V) BIASES ARE SHOWN

| Bias             | $x$ | $V_G$ | $G_{m_x}$ | $G_{d_x}$ | $G_{m2_x}$ | $G_{md_x}$ | $G_{d2_x}$ | $G_{m3_x}$ | $G_{m2d_x}$ | $G_{md2_x}$ | $G_{d3_x}$ |

|------------------|-----|-------|-----------|-----------|------------|------------|------------|------------|-------------|-------------|------------|

| $V_{G1} = -0.5$  | 1   | -0.5  | 78m       | 4.0m      | 130m       | 15m        | 0.10m      | -130m      | -19m        | -2.2m       | 0.025m     |

| $V_{SEP} = 0.3$  | 2   | -0.8  | 4.4m      | 0.15m     | 22m        | 2.4m       | 0.09m      | 140m       | 21m         | 0.96m       | -0.025m    |

| $V_{G1} = -0.1$  | 1   | -0.1  | 120m      | 7.1m      | 1.8m       | 3.5m       | -1.0m      | -260m      | -49m        | -0.72m      | 0.42m      |

| $V_{SEP} = 0.65$ | 2   | -0.75 | 9.7m      | 0.31m     | 55m        | 5.8m       | 0.16m      | 260m       | 38m         | 1.5m        | -0.027m    |

sign reversal in the second-order terms in (1) at higher gate biases. The secondary transistor is biased near pinchoff where the second- and third-order distortion have a positive sign. The primary transistor is biased beyond the point where the sign of the second-order terms change sign so that second- and third-order distortion of this transistor have a negative sign. Therefore, it is possible to cancel second- and third-order distortion simultaneously and, hence, the baseband impedance effects and intermodulation levels are minimized.

A slice of Fig. 6 at  $V_{SEP} = 0.65$  V is shown in Fig. 8. There is a good null near  $V_{G1} = -0.1$  V, though not quite as wide as that seen in Fig. 7. However,  $\Delta\text{IM3}$  is much smaller at this high gate bias so there is less baseband impedance susceptibility. This can be understood by noting that the derivative superposition nulls the third- and second-order distortion at this bias, as seen in Fig. 8(a). In addition, a greater degree of IM3 cancellation was observed in the null. Although this bias draws more drain current, it has more gain and lower intermodulation and, hence, the third-order intercept IP3 is higher. Thus, the ratio of IP3 to power consumption is similar for both biases, although the low  $\Delta\text{IM3}$  bias had a narrower null. The 1-dB saturation power is slightly improved over a single transistor amplifier for both biases.

The coefficients of nonlinear drain current (10) for both the conventional and low  $\Delta\text{IM3}$  bias are shown in Table I. These were extracted using a method similar to that in [9]. It can be seen that, for both the bias conditions, the third-order terms will be reduced. It is possible to calculate that  $c_0$  will be large for the conventional bias, and small for the low  $\Delta\text{IM3}$  bias. This shows that the theory correctly predicts that the baseband impedance effects will be smaller for the low  $\Delta\text{IM3}$  bias.

### C. Baseband Amplifier

A baseband amplifier accommodates signals ranging from near dc up to high frequencies. Apart from amplifying baseband signals, they have applications as ADC preamplifiers and as cable television boosters. A key feature of these amplifiers, of relevance to their distortion performance, is that second-order products at difference frequencies are likely to fall inside the passband of the amplifier. Therefore, the baseband impedance is not  $0 \Omega$ , but is usually equal to the load impedance.

This has an important consequence if the derivative superposition technique is to be employed in a baseband amplifier. The conventional bias region for derivative superposition amplifiers that gives a wide IM3 null, as shown in Fig. 7, has a large and positive  $\Delta\text{IM3}$ . This indicates that when the baseband impedance equals the load impedance, the intermodulation level indicated by the figure-of-merit IM3 will be changed in accordance with the figure-of-merit  $\Delta\text{IM3}$ . Thus, the null will almost

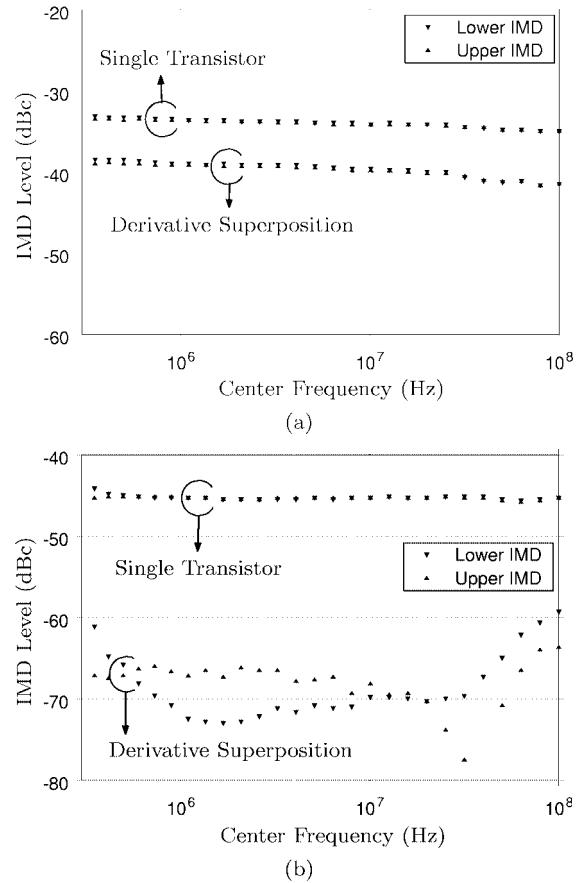

Fig. 9. Intermodulation levels of the baseband amplifier with  $V_D = 2$  V, input levels of  $V_s = 0.11$  V, and  $50\Omega$  load. (a) Conventional derivative superposition bias ( $V_{G1} = -0.5$ ,  $V_{SEP} = 0.3$ ). (b) Low  $\Delta\text{IM3}$  bias ( $V_{G1} = -0.1$ ,  $V_{SEP} = 0.65$ ).

completely disappear in this case and the linearity will not be substantially improved. This prediction was confirmed by measurement.

A solution to this problem is to bias in the region where there is still a good IM3 null, but where  $\Delta\text{IM3}$  is small so that the baseband impedance has little effect. This is the situation previously referred to in Fig. 8.

The circuit of the baseband amplifier was as shown in Fig. 4. The linearization performance when the amplifier is biased in the high  $\Delta\text{IM3}$  region and the low  $\Delta\text{IM3}$  region are compared in Fig. 9. The amplifier has a bandwidth of 300 kHz to 100 MHz with less than 1-dB variation in gain. The lower frequency limit can be extended by lowering the corner frequency of the bias networks or by using dc coupling.

The IM3 reduction when the amplifier is biased in the commonly used region with high  $\Delta\text{IM3}$  [see Fig. 9(a)] is less than

Fig. 10. Intermodulation levels of the 900-MHz amplifier with  $V_D = 2$  V and tone input levels of  $V_s = 0.9$  V. (a) Conventional derivative superposition bias ( $V_{G1} = -0.55$ ,  $V_{SEP} = 0.15$ ). (b) Low  $\Delta\text{IM3}$  bias ( $V_{G1} = -0.3$ ,  $V_{SEP} = 0.4$ ).

7 dB. When the amplifier is biased in the low  $\Delta\text{IM3}$  region [see Fig. 9(b)], the IM3 reduction is greater than 14 dB over the whole band.

#### D. RF Amplifier

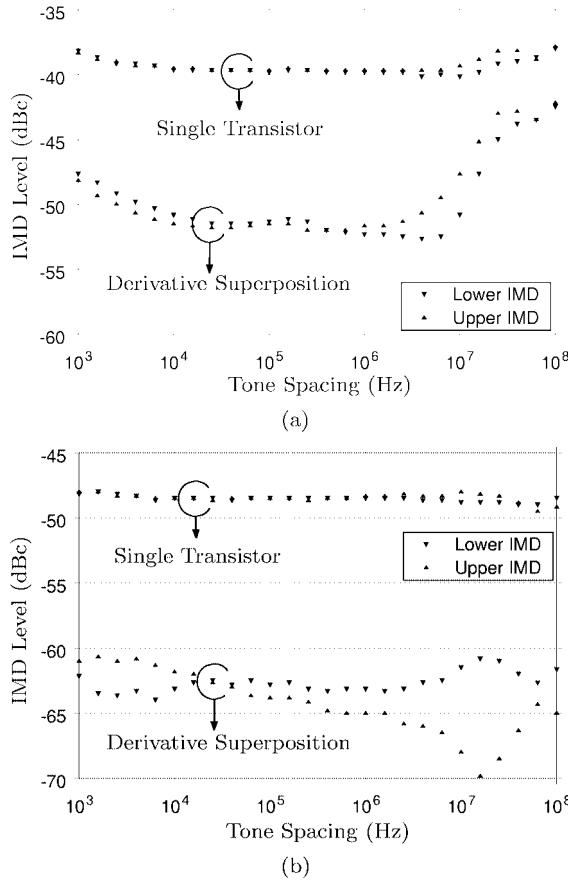

A 900-MHz derivative superposition amplifier was constructed. The circuit was similar to Fig. 4, except that an input matching network was added. This amplifier is used to illustrate the effects of baseband impedance on intermodulation in bandpass derivative superposition amplifiers. An  $LC$  bias network was used at the outputs of the devices. The intermodulation levels were measured with varying  $V_{G1}$  and  $V_{SEP}$  to produce graphs for IM3 and  $\Delta\text{IM3}$  similar to those in Fig. 6. From these graphs, two biases were selected for testing the intermodulation levels with varying tone spacing.

The first bias used is the conventional bias, giving a broad null, but with a high susceptibility to baseband impedance effects, as illustrated for the 50-MHz amplifier in Fig. 7. The resulting intermodulation levels versus tone spacing are shown in Fig. 10(a). The improvement in intermodulation levels by using derivative superposition over a single transistor circuit is better than 10 dB for small bandwidth signals. However, the improvement rapidly degrades for bandwidths greater than a few megahertz due to the changing baseband impedance. At bandwidths greater than 20 MHz, the improvement is less than 5 dB. The rise in intermodulation levels at small tone spacings is thought

to be due to device-level mechanisms such as thermal or trapping effects.

The second bias used is the low  $\Delta\text{IM3}$  bias, where the primary transistor has a higher gate voltage so that the second-order terms in the IM3 are small, as demonstrated in the situation shown in Fig. 8. The intermodulation levels over tone spacing are far less variable at this bias, as seen in Fig. 10(b). The improvement in intermodulation is better than 12 dB, over the measured tone spacing, out to 100 MHz. This represents a very wide bandwidth of linearization for a 900-MHz amplifier.

## V. CONCLUSION

The distortion of FET amplifiers is often sensitive to the impedance presented to the drain of the device at baseband frequencies. This fact has been used to linearize a single-FET amplifier simply by selecting a suitable baseband impedance. The effects of baseband impedance on derivative superposition amplifiers have been studied, and a bias has been found where there is both a good intermodulation null and little dependence of the distortion on baseband impedance. This was shown to be crucial to the successful application of the derivative superposition technique to baseband amplifiers. A 900-MHz derivative superposition amplifier was used to verify the baseband impedance effects, showing the improvement in linearization bandwidth that can be achieved by selecting a suitable bias.

## APPENDIX

The coefficients in the intermodulation (5) are as follows from [7]:

$$c_0 = \frac{1}{2} \left( G_{m2} + \frac{1}{2} G_{md}(A + A^*) + G_{d2}AA^* \right) \cdot (G_{md} + 2G_{d2}A) \quad (11)$$

$$c_1 = -\frac{3}{4} \left( G_{m3} + \frac{1}{3} G_{m2d}(2A + A^*) + \frac{1}{3} G_{md2}(2AA^* + A^2) + G_{d3}A^2A^* \right) \quad (12)$$

$$c_2 = \frac{1}{4} (G_{m2} + G_{md}A + G_{d2}A^2) \cdot (G_{md} + 2G_{d2}A^*) \quad (13)$$

where  $A = -G_m Z_o(\omega_c)$  is the gain at the fundamental frequency.

## ACKNOWLEDGMENT

The authors thank the Commonwealth Scientific and Industrial Research Organization (CSIRO), Telecommunications and Industrial Physics, Sydney, Australia, and Dr. J. W. Archer, CSIRO, for their support.

## REFERENCES

- [1] A. M. Crosmun and S. A. Maas, "Minimization of intermodulation distortion in GaAs MESFET small-signal amplifiers," *IEEE Trans. Microwave Theory Tech.*, vol. 37, pp. 1411–1417, Sept. 1989.

- [2] G. Hau, T. B. Nishimura, and N. Iwata, "A highly efficient linearized wide-band CDMA handset power amplifier based on predistortion under various bias conditions," *IEEE Trans. Microwave Theory Tech.*, vol. 49, pp. 1194–1201, June 2001.

- [3] C.-W. Fan and K.-K. Cheng, "Theoretical and experimental study of amplifier linearization based on harmonic and baseband signal injection technique," *IEEE Trans. Microwave Theory Tech.*, vol. 50, pp. 1801–1806, July 2002.

- [4] D. R. Webster, J. B. Scott, and D. G. Haigh, "Control of circuit distortion by the derivative superposition method," *IEEE Microwave Guided Wave Lett.*, vol. 6, pp. 123–125, Mar. 1996.

- [5] W. Bosch and G. Gatti, "Measurement and simulation of memory effects in predistortion linearizers," *IEEE Trans. Microwave Theory Tech.*, vol. 37, pp. 1885–1890, Dec. 1989.

- [6] N. B. de Carvalho and J. C. Pedro, "Two-tone IMD asymmetry in microwave power amplifiers," in *IEEE MTT-S Int. Microwave Symp. Dig.*, vol. 1, Boston, MA, 2000, pp. 445–448.

- [7] J. Brinkhoff and A. E. Parker, "Effect of baseband impedance on FET intermodulation," *IEEE Trans. Microwave Theory Tech.*, vol. 51, pp. 1045–1051, Mar. 2003.

- [8] ———, "Implication of baseband impedance and bias for FET amplifier linearization," in *IEEE MTT-S Int. Microwave Symp. Dig.*, vol. 2, Philadelphia, PA, 2003, pp. 781–784.

- [9] J. C. Pedro and J. Perez, "Accurate simulation of GaAs MESFET's intermodulation distortion using a new drain-source current model," *IEEE Trans. Microwave Theory Tech.*, vol. 42, pp. 25–33, Jan. 1994.

- [10] J. F. Sevic, K. L. Burger, and M. B. Steer, "A novel envelope-termination load-pull method for ACPR optimization of RF/microwave power amplifiers," in *IEEE MTT-S Int. Microwave Symp. Dig.*, vol. 2, Baltimore, MD, 1998, pp. 723–726.

James Brinkhoff (S'02) was born in 1979. He received the B.E. degree from the University of Tasmania, Tasmania, Australia, in 2001, and is currently working toward the Ph.D. degree at Macquarie University, Sydney, N.S.W., Australia.

His honors project investigated the use of SiGe HBTs for wide-band low-noise amplifiers. His research interests include monolithic microwave integrated circuit (MMIC) design, effects of microwave circuit nonlinearity on communication systems, amplifier linearization, and nonlinear circuit analysis.

**Anthony Edward Parker** (S'84–M'84–SM'95) received the B.Sc., B.E., and Ph.D. degrees from The University of Sydney, Sydney, Australia, in 1983, 1985, and 1992, respectively.

In 1990, he joined Macquarie University, Sydney, Australia, where he is currently the Head of the Electronics Department. He is involved with a continuing project on pulsed characterization of microwave devices and design of low-distortion communications circuits. He has worked as a consultant with several companies including M/A-COM, Lowell, MA, and Agilent Technologies Inc., Santa Rosa, CA. He has developed accurate circuit simulation techniques, such as used in the Parker–Skellern FET model. He authored or coauthored over 100 publications.

Prof. Parker is a member of the Institution of Telecommunications and Electronic Engineers, Australia. He served on the Technical Committees for the 2000 IEEE Asia–Pacific Microwave Conference, Sydney, Australia, and as technical co-chair for the 2001 IEEE Symposium on Circuits and Systems, Sydney, Australia.

**Martin Leung** (S'02) was born in 1980. He received the B.E. degree from the University of Canberra, Canberra, Australia, in 2002, and is currently working toward the Ph.D. degree at the University of Sydney, Sydney, N.S.W., Australia.

He was a Research Assistant with the Transistor-Modeling Group, Macquarie University.